2. Alat dan Bahan

[Kembali]

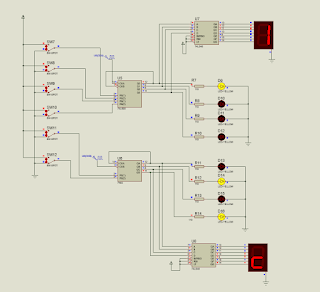

Gambar 3.1 Rangkaian percobaan 2a menggunakan simulasi pada proteus

Gambar 3.2 Rangkaian percobaan 2b menggunakan simulasi pada proteus

Gambar 3.2 Rangkaian percobaan 2a pada Delorenzo

Pada rangkaian Asynchronous counter pada percobaan 2, terdapat input yang terdiri dari 6 sakelar, dimana sakelar ini dapat terhubung ke VCC (memberikan logika 1) dan dapat juga terhubung ke ground (unruk memberikan logika 0). Sakelar tersebut kemudian dihubungkan dengan counter dengen IC 74LS90 dan 7493.

Pada percobaan 2a, kaki input CKA dan CKB dihubungkan ke clock, sedangkan pada percobaan 2B, hanya kaki CKB yang terhubung ke clock dan kaki CKA dihubungkan dengan output Q0 dari counter 74LS90. Begitu juga dengan CKA dan CKB dari counter 7493.

Rangkaian di atas akan mengeluarkan logika 4 bit yang mana kemudian output 4 bit dari masing-masing counter akan dihubungkan dengan decoder yang mengubah logika 4 bit menjadi 7 bit dan kemudian output 7 bit tersebut dihubungkan ke 7-segment untuk menampilkan outputnya. selain dihubungkan dengan seven segment, output dari counter juga dihubungkan dengan LED yang mana ketika logika 1 maka LED akan hidup dan ketika logika 0 LED akan mati.

Pada counter 74LS90, R0(1) dan R0(2) berfungsi sebagai Reset dan R9(1) serat R9(2) berfungsi sebagai Set. Oleh karena itu, ketik R0(1) dan R0(2) diberikan logika 1, maka output akan di reset ke dalam logika 0 sehingga seven segment akan menunjukkan angka 0 dan LED tidak menyala, jadi dalam kondisi ini ketika R9(1) atau R9(2) diberikan logika 1 maka output Q0, Q1, Q2 dan Q3 akan low atau berlogika 0. Sedangkan ketika R9(1) dan R9(2) diberikan logika 1, maka output kan di set menjadi nilai maksimal dari bit yang dihitung yaitu 9 (1001), dan dalam kondisi ini, ketika R0(1) atau R0(2) diberika logika apapun (don't care) maka output dari Q0, Q1, Q2, dan Q3 berturut-turut adalah 1, 0, 0,1. Sedangkan ketika salah satu dari R0 dan R9, seperti R1(0) dan R9(1) berlogika 1, maka outputnya akan bergantian berlogika 1 (dalam posisi count). Sehingga pada seven segment akan terlihat outptu menghitung tetapi tidak berurutan. Akan tetapi ketika CKA dihubungkan dengan output Q0 sebagaimana pada percobaan 2b, maka seven segment akan menampilkan hitungan 0-9 atau 0000-1001 secara berurutan.

Pada counter 7493, hanya terdapat R0(1) dan R0(2) yang mana ketika diberikan logika 1, amak akan mereset semua output menjadi logika 0 dan seven segment akan menampilkan angka 0 serta LED tidak akan menyala. Sedangkan ketika salah satu dari R0(1) dan R0(2) berlogika 1 maka outputnya akan dalam posisi count atau menghitung naik tetapi tidak berurutan. Akan tetapi ketika CKA dihubungkan dengan Q(0) maka seven segmen akan menampilkan hitungan naik dari 0000- 1111.

6. Analisa

[Kembali]

1. Jelaskan perbedaan percobaan 2a dengan percobaan 2b

Jawab:

Perbedaan antara percobaan 2a dengan percobaan 2b terletak pada input CLK-nya. Pada percobaan 2a, CLK1 (CKA) dan CLK2 (CKB) sama-sama terhubung ke clock. Sedangkan pada percobaan db, clocknya (CLK1 dan CLK2) mempunyai input yang berbeda. Clock 1 (CLK1) terhubung ke clock, sedangkan clock 2 (CLK2) terhubung ke output Qa dari counter. Hal ini berlaku untuk kedua jenis IC counter yang digunakan pada percobaan 2a dan 2b.

2. Mengapa terjadi perbedaan output pada percobaan 2a dan 2b

Jawab:

Pada percobaan 2a, output menghitung naik secara tidak berurutan, sedangkan pada percobaan 2b, output menghitung naik secara berurutan. Hal tersebut terjadi karena pada dasarnya IC74LS90 akan menghitung naik secara berurutan ketika clock 1 dan 2 diberikan input yang berbeda. sedangkan pada IC74LS48 counter akan menghitung naik untuk bilangan genap secara berurutan. Dimana pada percobaan 2b, ketika CK2 terhubung ke Qa maka menyebabkan rangkaian mejadi full asinkron (aynchronous), sedangkan pada percobaan 2a, hanya 3 flip flop terakhir yang asynchronous.

7. Link Download

[Kembali]

.jpeg)

Tidak ada komentar:

Posting Komentar