2. Alat dan Bahan

[Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

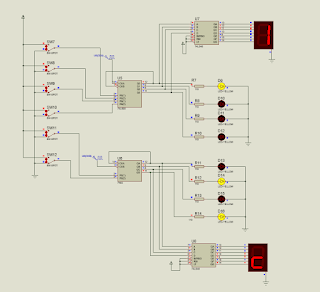

Pada rangkaian percobaan 3 digunakan 7 switch yang berfungsi sebagai input dan masing-masingnya terhubung ke ground untuk meberikan logika 0 dan terhubung ke VCC untuk memberikan logika 1. Masing- masing switch kemudian dihubungkan ke decoder IC74LS47 atau BCD(Binary code decimal). IC74LS47 ini memiliki 4 input dan 7 input yang terhubung ke seven segment common anoda. Pada rangkaian ini digunakan seven segment common anoda dikarenakan output IC74LS47 merupakan aktif rendah.

Adapun konfigurasi pin dari IC74LS47 adalah sebagai berikut:

1. Pin input, terdiri dari empat Pin, yaitu A, B, C, dan D. Input ini bekerja pada logika 1 (high)

2. Pin output, terdiri dari 7 output, yaitu QA, QB, QC, QD, QE, QF dan QG. ketujuh pin output ini bekerja pada aktif rendah sehingga harus dihubungkan dengan seven segment common anoda.

3. Pin LT (lamp test), pin ini berfungsi untuk mengetes kondisi LED pada seven segmen dan juga berfungsi menset ketika diberikan aktif rendah sehingga menampilkan angka 8 pada seven segment.

4. Pin RBI (Ripple Blanking Input), pin ini memberikan pengaruh yang sama dengan RBO yaitu mematikan keluaran IC dari decoder. Akan tetapi, kinerja diambil alih oleh RBO dimana input RBO- Bi, dengan demikian input RBI dapat diabaiakan pada proses pencacahan angka seven segment pada decoder.

5. Pin BI/RBO (Blanking Input/ Ripple Blanking Output), pin ini meliki fungsi unnutk menahan data output atau mematikan display output. Ketika pin ini aktif, maka seven segment tidak akan aktif.

Pada IC74LS47, kaki LT, RBI, dan BI/RBO memiliki aktif rendah, sehingga agar ketiga pin ini tidak memeberikan pengaruh ke tampilan seven sefment, maka ketiga pin ini harus diberikan logika 1.

adapun tabel kebenaran dari IC74LS47 adalah sebagai berikut:

6. Analisa

[Kembali]

1. Analisa pengaruh LT, RBO, RBI

Jawab:

Ketika LT aktif, maka output yang ditunjukkan oleh seven segment adalah angka 8 atau outptu dari decoder semuanya berlogika 0.

Ketika RBO dan RBI aktif, maka seven segment tidak akan menunjukkan angka apapun atau mati.

Dimana pada rangkaian percobaan 2, LT, RBI, dan RBO mempunyai jenis aktid low sehingga akan aktif ketika diberikan logika 0.

2. Analisa pengaruh BCD decoder to seven segment pada rangkaian

Jawab:

Seven segment tidak akan mampu membaca lansung input yang diberika oleh switchq, sehingga diperlukan BCD decoder untuk menerjemahkannya. BCD decoder memunyai atau mendapatkan input 4 bit. Kemudian input 4 bit tersebut diolah menjadi 7 bit dan dihubungkan ke seven segment, sehingga seven segment dapat menampilkan output dari decoder. Selain mempunyai 4 input A, B, C, dan D, BCD decoder juga mempunyai input LT, RBI, dan RBO. Agar seven segment dapat menunjukkan output yang sesuai dengan dyang diberikan oleh A, B, C , dan D maka LT, RBI, RBO harus dinonaktifkan atau diberikan logika 1.

7. Link Download

[Kembali]

.png)

.png)

.png)

.png)

.jpeg)

.jpeg)